A debounce refers to the glitches present in a physical circuit when a button or switch is triggered.

When pressed, the signal oscillates for a short time before stabilizing.

A debounce circuit is designed to:

- Filter out glitches

- Produce a clean square wave output

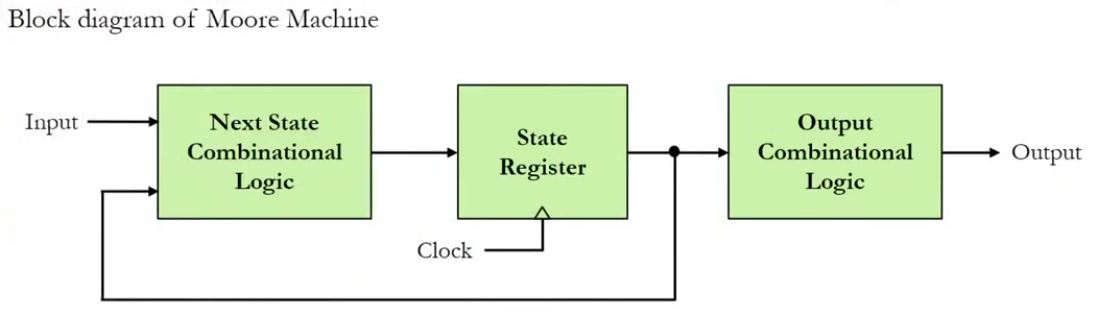

This circuit can be implemented as a Moore Machine.

Concept

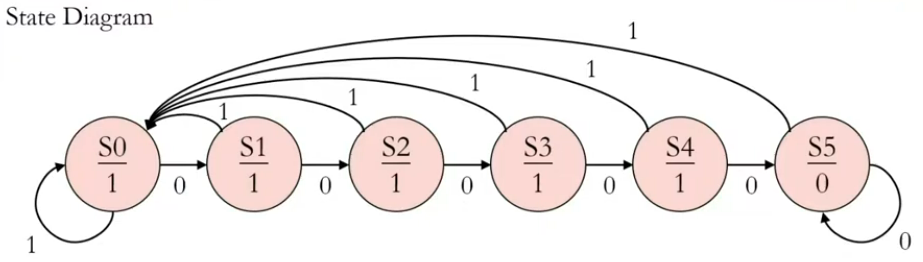

- The idle state (before button is pressed) is S0.

- The following states (S1 → Sn) act as a stabilizing filter.

- More states = better debounce effect but also more delay.

State Diagram

Block Diagram

Verilog Implementation

module Debounce_Circuit(

input Din, clk, reset,

output reg Dout

);

reg [2:0] cs, ns;

// Next State Combinational Logic

always @(*) begin

case(cs)

3'd0: ns = (Din) ? 3'd0 : 3'd1;

3'd1: ns = (Din) ? 3'd0 : 3'd2;

3'd2: ns = (Din) ? 3'd0 : 3'd3;

3'd3: ns = (Din) ? 3'd0 : 3'd4;

3'd4: ns = (Din) ? 3'd0 : 3'd5;

3'd5: ns = (Din) ? 3'd0 : 3'd5;

default: ns = 3'd0;

endcase

end

// State Register

always @(posedge clk or negedge reset) begin

if (!reset)

cs <= 3'd0;

else

cs <= ns;

end

// Output Combinational Logic

always @(*) begin

case(cs)

3'd0,

3'd1,

3'd2,

3'd3,

3'd4: Dout = 1'b1; // Stable high before pressed

3'd5: Dout = 1'b0; // Button stable pressed

default: Dout = 1'b1;

endcase

end

endmodule