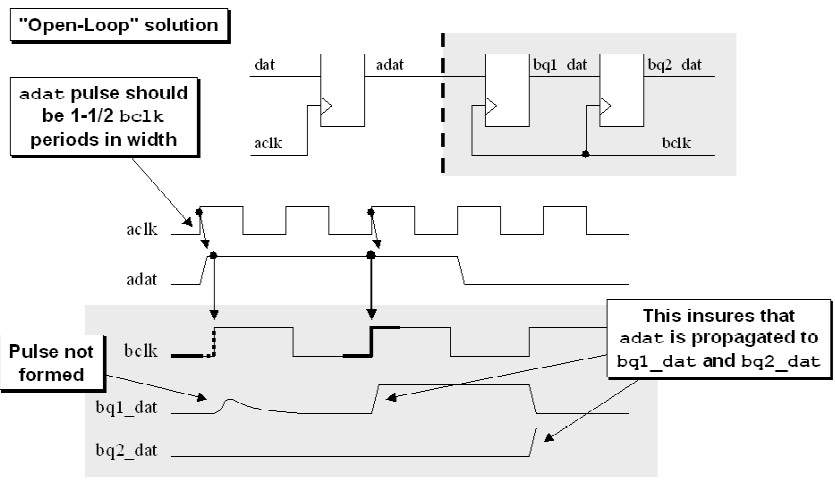

An open-loop solution is one method for transferring signals across Clock Domain Crossing (CDC) boundaries using synchronizers.

In this approach, the CDC signal is asserted (held high) for a duration longer than one full cycle of the receiving clock.

This ensures that the receiving clock will sample the signal at least once — and often twice — during its active period.

🧮 Timing Requirement

The minimum pulse width for a CDC signal should be:

≥ 1.5 × the period of the receiving clock frequency

This is equivalent to ensuring that the signal remains stable for three destination clock edges (the “three-edge” requirement).

When this condition is met, the signal will reliably be captured by the receiving clock domain without the need for feedback or acknowledgment.

⚙️ When to Use Open-Loop Sampling

Open-loop synchronization can be safely used only when:

-

The relative clock frequencies between the source and destination domains are fixed and well understood, and

-

The timing relationship has been thoroughly analyzed to ensure compliance with the “three-edge” requirement.

✅ Advantages

-

High speed:

The open-loop solution is the fastest way to transfer signals across CDC boundaries. -

No acknowledgment required:

The sender does not need to wait for confirmation from the receiving domain.

⚠️ Disadvantages

-

Risk of misuse:

Another engineer might mistake the design for a general-purpose CDC solution, leading to potential reliability issues in future revisions. -

Design changes:

If clock frequencies or timing relationships change later, the original analysis may become invalid, causing synchronization failures.

To mitigate these risks, it’s good practice to add a SystemVerilog Assertion (SVA) that monitors the input pulse width and ensures it always satisfies the “three-edge” rule.

🧩 Summary

| Aspect | Open-Loop Solution |

|---|---|

| Speed | Very fast (no acknowledgment) |

| Complexity | Low |

| Reliability | Dependent on fixed timing analysis |

| Risk | Failure if design parameters change |

| Best Practice | Verify using SystemVerilog assertions for pulse width ≥ 1.5× receiving clock period |