In a Multi-Cycle Path (MCP) formulation with feedback, the synchronized enable signal from the receiving clock domain is passed back to the sending clock domain as an acknowledge (ACK) signal.

This creates a closed-loop handshake ensuring that new data is only sent after the previous transfer has been safely received.

⚙️ How It Works

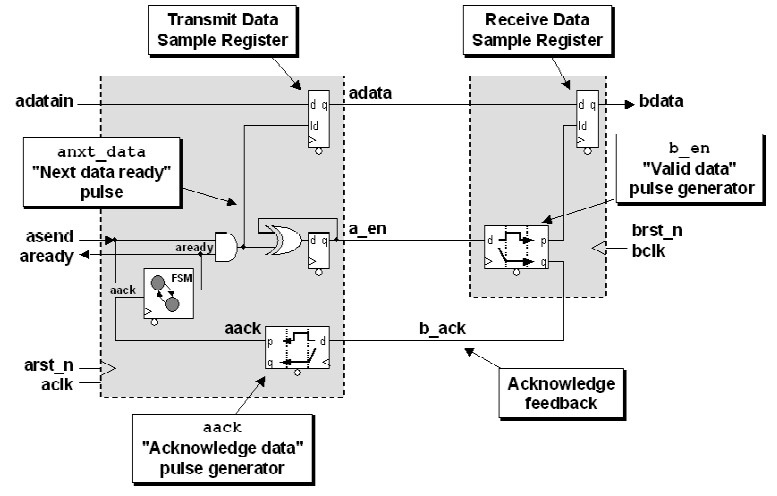

As shown in Figure 21 (conceptually), the system consists of:

a_clk— sending clock domainb_clk— receiving clock domainasend— control signal sent from the sender to initiate a data transferb_ack— acknowledge signal generated in the receiving domainaack— synchronized version ofb_ackin the sending domainaready— a ready signal indicating the sender can send new data againadatain— multi-bit data word being transferred

🔁 Step-by-Step Operation

-

Sender initiates a transfer:

- The sending domain asserts

asendalong with valid data onadatain.

- The sending domain asserts

-

Receiver captures data:

- The

asendtoggle is synchronized into the receiving domain through the MCP synchronizer. - The receiving domain then captures the unsynchronized data once the synchronized enable pulse is detected.

- The

-

Receiver sends back acknowledgment:

- After successfully capturing the data, the receiver toggles or asserts an acknowledge signal (

b_ack).

- After successfully capturing the data, the receiver toggles or asserts an acknowledge signal (

-

Sender receives acknowledgment:

- The

b_acksignal is sent back through another synchronizer to the sending domain, producingaack.

- The

-

Sender updates ready signal:

- A small READY–BUSY FSM in the sending domain uses

aackto set aareadyflag high. aready = 1indicates the receiver is ready for the next data word.

- A small READY–BUSY FSM in the sending domain uses

-

Next data transfer:

- The sender waits until

aready= 1 before changingadatainand re-assertingasendfor the next transfer.

- The sender waits until

🧠 Key Principle

The sender must never update

adatainuntil the receiver acknowledges that the previous word has been captured.

This ensures data integrity and prevents overwriting or metastable sampling.

✅ Advantages

| Advantage | Description |

|---|---|

| Reliable handshake | Guarantees the receiver has captured data before new data is sent |

| Automatic synchronization | Each direction (forward & backward) uses standard synchronizers |

| No fixed timing assumptions | Works across any relative clock frequencies |

| Simple implementation | Only requires a small FSM for ready/busy management |

⚠️ Design Notes

- The READY–BUSY FSM in the sender typically has one active state (BUSY) between sending and acknowledgment.

- This design assumes the receiver is always ready for the next transfer (i.e., no back-pressure mechanism needed).

- The technique can be extended with additional logic if the receiver needs to throttle or pause transfers.

🪄 Typical Sequence Diagram

| Step | Sender (a_clk) |

Receiver (b_clk) |

|---|---|---|

| 1 | Assert asend with adatain |

— |

| 2 | — | Capture adatain on synchronized pulse |

| 3 | — | Toggle b_ack |

| 4 | Receive aack (synced back) |

— |

| 5 | aready = 1 → safe to send next word |

— |

🧩 Summary

- MCP with feedback adds a synchronization loop to confirm successful data transfer.

- It’s ideal for event-driven or sporadic multi-bit transfers across unrelated clock domains.

- Combines the speed of MCP (multi-bit unsynchronized transfer) with the safety of a closed-loop handshake.

Would you like me to include a timing diagram (like Figure 21) to visualize the handshake sequence between asend, adatain, b_ack, and aack? It can make this closed-loop concept much clearer.